Document Number: MPC5748GLCEVBUG

Rev. 0, 05/2016

# MPC5748G Low Cost EVB User Guide

## **Contents**

| 1. | INTRODUCTION                                    | 3  |

|----|-------------------------------------------------|----|

| 2. | LCEVB FEATURES                                  | 3  |

| 2  | 2.1. Differences to the Customer EVB            | 4  |

| 3. | CONFIGURATION OVERVIEW                          | 6  |

| 4. | INITIAL SETUP                                   | 7  |

| 4  | 4.1. Power Supply Configuration                 | 7  |

|    | 4.1.1. Power Input Connector                    |    |

|    | 4.1.2. Power Switch                             |    |

|    | 4.1.3. Power Status LED.                        |    |

|    | 4.1.4. MCU and Peripheral Voltage Configuration |    |

| 4  | 4.2. Reset Control (SW3)                        |    |

|    | 4.2.1. Reset LEDs                               |    |

| 4  | 4.3. MCU Clock Configuration                    |    |

| 4  | 4.4. Debug Connector (P1)                       |    |

|    | 4.4.1. Debug Connector Pinout                   |    |

| 5. | COMMUNICATIONS & MEMORY INTERFACES:             | 11 |

| 5  | 5.1. CAN Interfaces (P2, P3)                    | 11 |

| 5  | 5.2. LIN Interfaces (P6, P7)                    | 12 |

| 5  | 5.3. USB RS232 Serial Interface (P11)           | 12 |

| 5  | 5.4. USB HOST Interface (P4)                    |    |

| 5  | 5.5. Ethernet Interface (P5)                    |    |

| 5  | 5.6. FlexRay (P8, P9, P10)                      | 13 |

| 6. | USER INTERFACE (I/O)                            | 14 |

| 6  | 5.1. GPIO Matrix                                | 14 |

| 6  | 5.2. User Switches (SW4, SW5)                   | 15 |

| 6  | 5.3. Hex Encoded Switch (SW1)                   | 15 |

| 6  | 5.4. User LED's (DS1, DS2, DS3, DS4)            | 16 |

| 6  | 5.5. ADC Input Potentiometer (RVAR, RV1)        |    |

| 7. | MCU PORT PIN LCEVB FUNCTIONS                    | 17 |

| 8. | APPENDIX                                        | 18 |

|    |                                                 |    |

#### 1. Introduction

This user guide details the setup and configuration of the NXP MPC5748G Low Cost Evaluation Board (hereafter referred to as the LCEVB). The LCEVB is intended to provide a mechanism for easy evaluation of the MPC5748G family of microcontrollers, and to facilitate basic hardware and software development.

Note that the LCEVB has a limited feature set compared to the main MPC574xG customer EVB and is intended for evaluation purposes. Customers moving to serious development activities are recommended to purchase the fully functional customer EVB which also has device specific daughter cards.

The LCEVB is intended for bench / laboratory use and has been designed using normal temperature specified components ( $+70^{\circ}$  C).

This product contains components that may be damaged by electrostatic discharge. Observe precautions for handling electrostatic sensitive devices when using the LCEVB.

The user guide is intended to be read alongside the respective MCU documentation available at www.nxp.com and includes:

- Reference Manuals

- Product Data Sheets

- Application notes

- Device Errata

#### 2. LCEVB Features

The LCEVB provides the following key features:

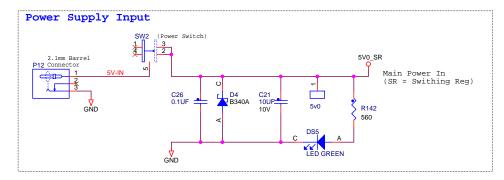

- Single 5 V DC external power supply input with on-board 3.3 V regulator. Power is supplied via a 2.1 mm barrel style power jack.

- Simple jumperless configuration (enhanced configuration is possible via 0 Ohm Resistors and optional jumpers if required).

- Master power switch and regulator status LED.

- USB Serial interface.

- 2 x High Speed CAN transceiver routed to 3-way headers.

- 2 x LIN interfaces routed to 3-way headers.

- Main clock supplied from on board crystal.

- User reset switch with reset status LED's.

- Ethernet PHY and RJ45 socket (configured for MII mode).

- USB Type A Host interface.

- 2 x FlexRay interfaces with standard 2-pin connectors.

- 14-pin JTAG connector.

- 4 user LED's wired to MCU ports.

- 2 user pushbutton switches wired to MCU ports.

- Hexadecimal encoded switch wired to 4 MCU ports.

- Simple potentiometer connected to analogue input channel.

#### 2.1. Differences to the Customer EVB

Note that the GPIO pins used for peripherals on the LCEVB are the same as those used on the customer EVB. This ensures maximum code compatibility between the 2 boards, making it easy to migrate from one board to the other

Table 1. Customer EVB vs LCEVB features

| Feature                         | Customer EVB                                                            | LCEVB                                             |

|---------------------------------|-------------------------------------------------------------------------|---------------------------------------------------|

| MCU Support                     | Custom MCU Daughtercards for                                            | Soldered 176QFP MPC5748G                          |

|                                 | multiple devices (socketed)                                             |                                                   |

| Power Supply                    | External 12 V                                                           | External 5 V (Caution)                            |

| On Board Regulators (and LED's) | 5 V, 3.3 V, 1.25 V (combination of Linear and /or Switching regulators) | 3.3 V Switching Regulator                         |

| Master Power Switch             | Yes                                                                     | Yes                                               |

| Reset Control                   | Reset button with MCU and External Reset LED's                          | Reset button with MCU and External Reset LED's    |

| USB FTDI Serial Interface       | Yes                                                                     | Yes                                               |

| CAN Physical Interfaces         | 2 (routed to 0.1" headers)                                              | 2 (routed to 0.1" headers)                        |

| LIN Physical Interfaces         | 2 (routed to Molex headers)                                             | 2 (routed to 0.1" headers)                        |

| FlexRay Physical Interfaces     | 2 (routed to 0.1" headers)                                              | 2 (routed to 0.1" headers)                        |

| Ethernet Physical Interface     | 1 (MII and RMII Support)                                                | 1 (MII only mode)                                 |

| USB Physical Interface          | 2 (USB Host and OTG)                                                    | 1 (USB Host)                                      |

| MLB Daughtercard Connector      | Yes                                                                     | No                                                |

| SAI Audio / TWRPI Connectors    | Yes                                                                     | No                                                |

| SDHC Connector                  | Full Size SDHC Socket                                                   | No                                                |

| Fast External Osc (FXOSC)       | Daughtercard Crystal * and SMA input connector                          | 40 MHz Crystal                                    |

| Slow External Osc (SXOSC)       | Daughtercard Crystal *                                                  | 32.768 KHz Crystal                                |

| CLKOUT signals available        | Yes (GPIO Matrix)                                                       | Yes (Standalone pads)                             |

| User LEDS                       | 4                                                                       | 4                                                 |

| User Pushbutton Switches        | 4                                                                       | 2                                                 |

| Hex Encoded Switch              | Yes                                                                     | Yes                                               |

| Test Potentiometer for ADC      | Yes                                                                     | Yes                                               |

| GPIO Matrix                     | All Available Pins not otherwise used for peripherals                   | Selection of Pins available from 5<br>GPIO Ports  |

| Debug                           | 14 Pin JTAG and 50 pin Nexus                                            | 14 Pin JTAG                                       |

| Configuration                   | Highly configurable via jumper shunts                                   | Fixed (limited configuration via 0 ohm resistors) |

<sup>\*</sup> Daughtercard crystals are typically 40 MHz for FXOSC and 32.768 KHz for SXOSC but may vary between daughtercards.

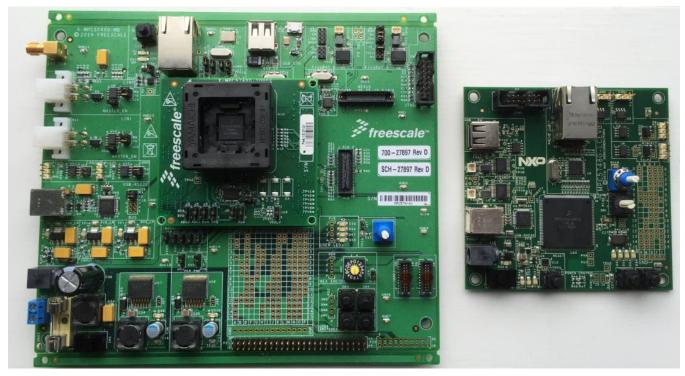

The figure below shows the customer EVB (left) next to the LCEVB(right).

Figure 1. Customer and LCEVB side by side

## 3. Configuration Overview

Out of the box, there is no configuration required for the LCEVB to function. Unlike the customer EVB, the LCEVB is primarily designed for a single mode of operation with no requirement for user configuration. If you wish to have a more flexible configuration the recommendation is that the fully configurable customer EVB is purchased.

There are however some jumper footprints and zero ohm resistors populated in positions that would normally have jumper headers fitted (for example on the MCU power supply lines and tracking to the peripheral interfaces). If required these can be de-soldered to modify functionality. Any such modification is done at the full risk of the user and no support or warranty repairs will be provided for a board that has been modified. Modifications should only be attempted by appropriately trained personnel using the correct equipment and Personal Protective Apparel

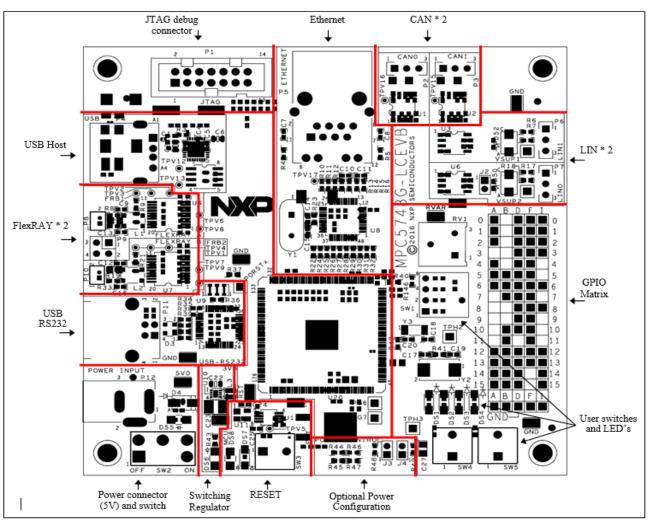

The diagram below gives an overview of the functional blocks of the LCEVB

Figure 2. EVB Functional Blocks

## 4. Initial Setup

This section details the power, reset, clocks, and debug configuration which is the minimum configuration needed in order to power ON the LCEVB.

#### 4.1. Power Supply Configuration

The LCEVB requires an external power supply voltage of 5 V DC, minimum 1 A. There is a single 3.3 V switching regulator on the LCEVB providing MCU and peripheral power.

#### **CAUTION**

Connecting a power supply with a voltage greater than 5 V will result in irrecoverable board damage. Check the power supply voltage before connecting the plug to the LCEVB.

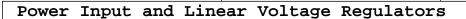

#### 4.1.1. Power Input Connector

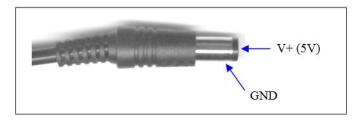

Power is supplied to the LCEVB via a 2.1 mm connector from the wall-plug mains adapter as shown below. Note – if a replacement or alternative adapter is used, care must be taken to ensure the 2.1 mm plug uses the correct polarisation as shown below:

Figure 3. 2.1 mm Power Connector

#### 4.1.2. Power Switch

Slide switch SW2 can be used to isolate the power supply input from the EVB voltage regulators if required.

- Moving the slide switch to the right (away from the power connector) will turn the EVB ON.

- Moving the slide switch to the left (towards the power connector) will turn the EVB OFF.

#### 4.1.3. Power Status LED

When power is applied to the LCEVB, two green LED's adjacent to the regulator and power connector show the presence of the supply voltages as follows:

- LED DS5 Indicates that the 5.0 V supply voltage is present

- LED DS6 Indicates that the 3.3 V switching regulator is functioning

If no LED's are illuminated when power is supplied to the LCEVB and the power switch is in the "ON" position, the power adapter may be faulty or there may be a fault with the LCEVB. If only one LED is illuminated there may be a short in that power supply rail – check there is nothing shorting on the EVB. If you continue to have problems, contact NXP for support.

#### **CAUTION**

In the event of a short on the regulator output (in which case one of the LED's would be off or dimly illuminated), the regulator and/or the shorted component will likely be hot.

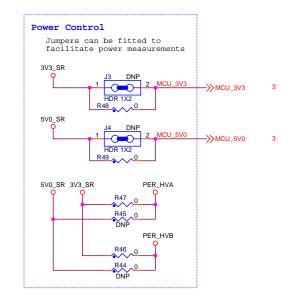

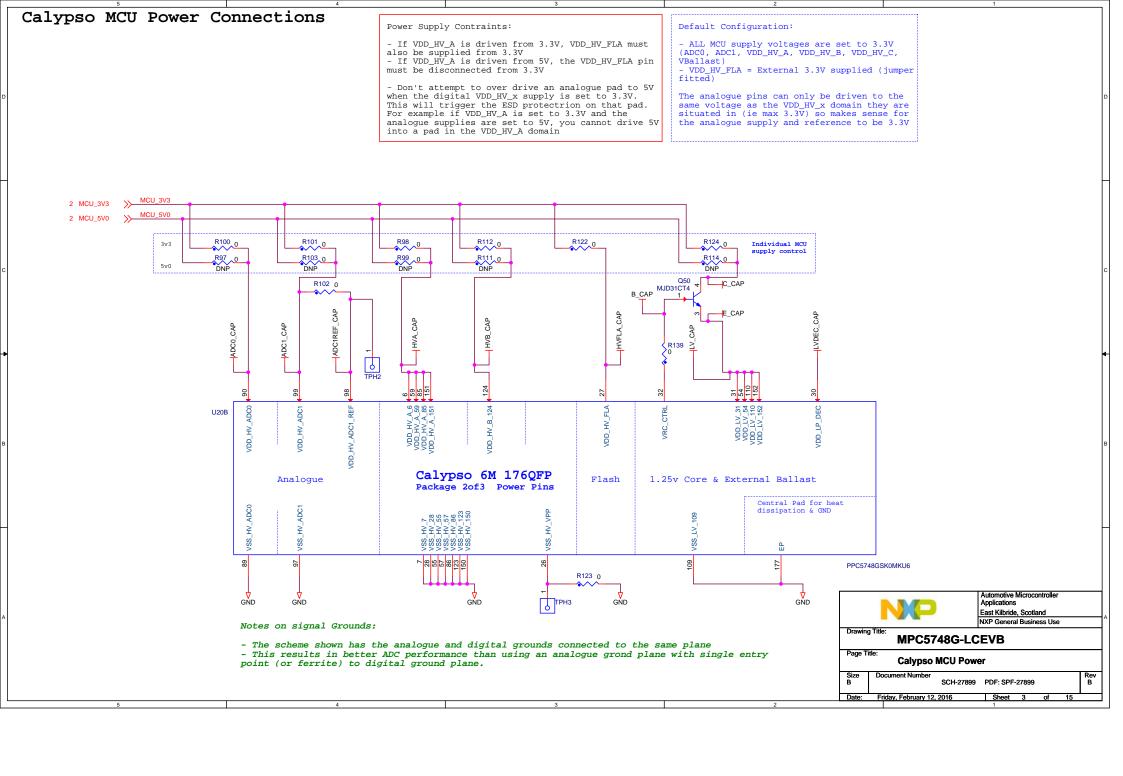

#### 4.1.4.MCU and Peripheral Voltage Configuration

The following MCU supply rails are connected to the 3.3 V switching regulator:

- VDD\_HV\_ADC0

- VDD HV ADC1

- VDD HV ADC1 REF

- VDD\_HV\_A

- VDD HV B

- VDD\_HV\_FLA

- External Ballast Transistor Supply

Similarly all of the peripheral interfaces (or the I/O power in the peripheral interface) are supplied from 3.3 V as is the reset circuitry and the voltage sense wire on the JTAG connector.

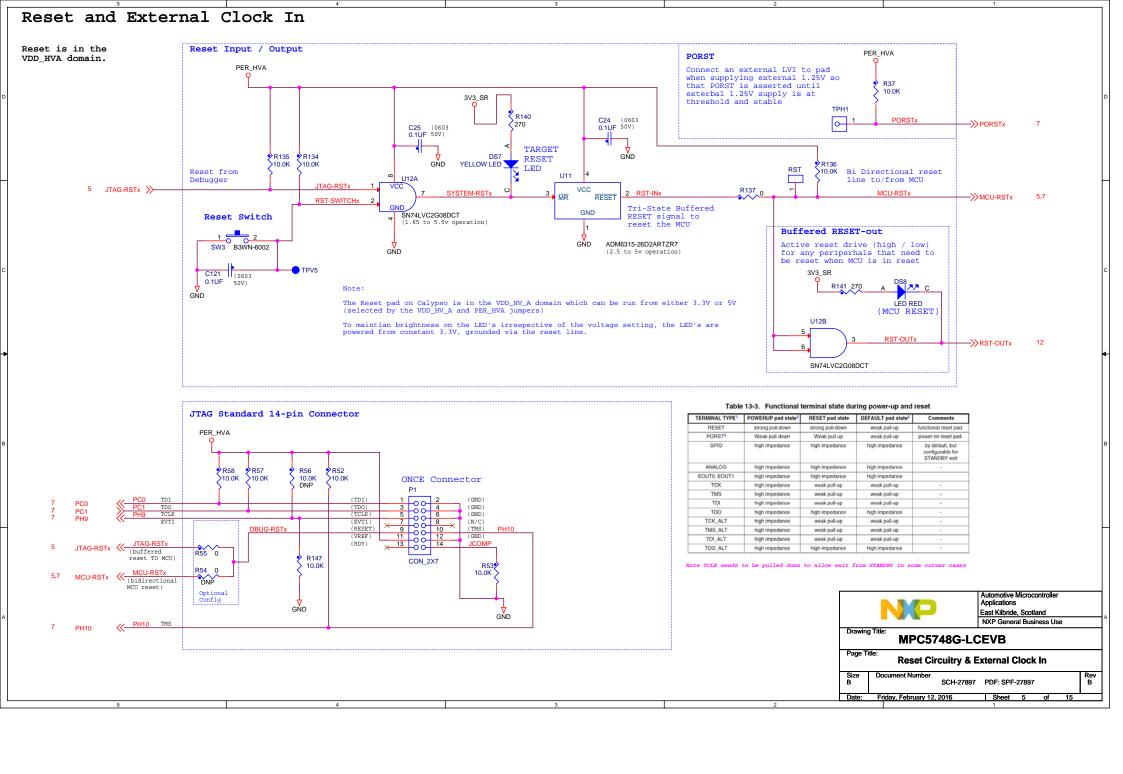

#### 4.2. Reset Control (SW3)

The reset circuitry is located in the bottom left quarter of the LCEVB next to the power switch

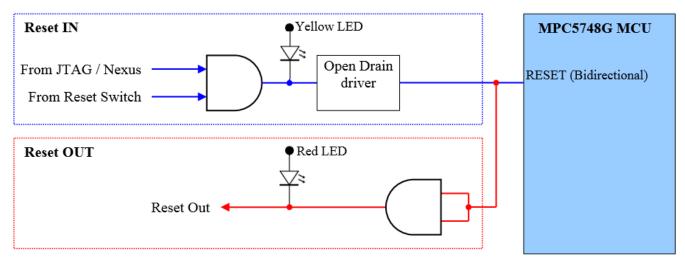

The MCU has a single bi-directional open drain Reset pin. Rather than connect multiple devices to the reset pin directly, a reset-in and reset-out buffering scheme has been implemented on the LCEVB as shown in Figure 4. The reset "in" from the reset switch (SW3) and the debug connectors are logically OR'd together using an AND gate and then connected to the buffer to provide an open-drain output.

The "reset-out" circuitry provides a buffered reset signal that can be used to drive any circuitry requiring a reset control from the MCU.

This scheme is not required if it is guaranteed that anything driving the reset pin has an open drain drive and that there is no significant output load on the MCU reset pin.

Figure 4. EVB Reset Control

#### 4.2.1. Reset LEDs

As can be seen above, there are two reset LED's that can be used to identify the source / cause of a reset: RED LED DS8 (titled "MCU") will illuminate if:

- The MCU issues a reset (in this condition ONLY this LED will be illuminated and LED DS1 will be off)

- There is a target reset (ie from the reset switch or from the debugger in which case LED DS1 will be ON)

YELLOW LED DS7 (titled "EXT") will illuminate when an external hardware device issues a reset to the MCU:

- The reset switch is pressed

- There is a reset being driven from one of the debug connectors

Table 2. Reset LED Decoding LED DS7 (Yellow) LED DS8 (Red) Description OFF OFF No Reset being issued from MCU or external logic **OFF** ON MCU has issued a reset External reset issued from switch or debug BUT not being issued to MCU ON **OFF** (check R137 has not been removed) ON ON External reset issued from reset switch or debug and has been issued to MCU

MPC5748G Low Cost EVB User Guide, User Guide, Rev. 0, 05/2016

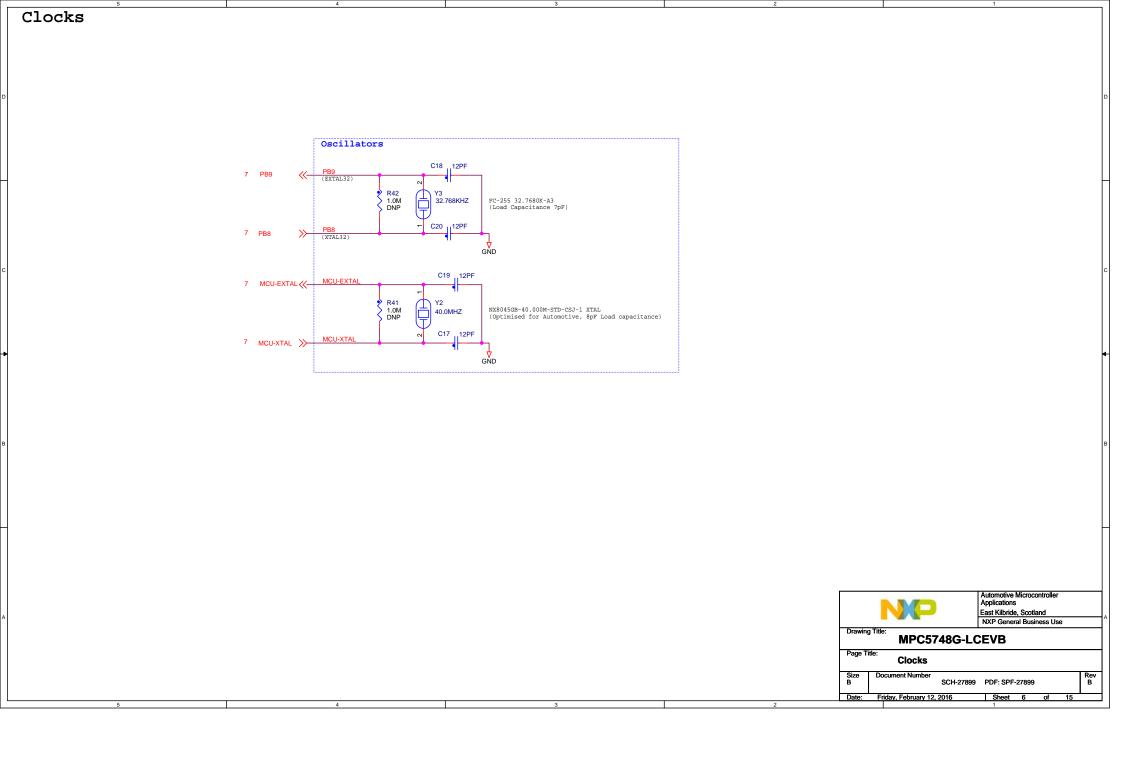

#### 4.3. MCU Clock Configuration

There is an external 40MHz crystal connected to the MCU Fast External Oscillator (FXOSC) pins EXTAL and XTAL.

There is also a 32.768 crystal connected to the MCU Slow External Oscillator (SXOSC) pins OSC32K\_EXTAL and OSC32K\_XTAL. This can be used for accurate time keeping.

There are 2 pads PG6 and PG7 (located just below the MCU) on the LCEVB to facilitate measurement of the CLKOUT1 and CLKOUT0 signals.

Note – there is no external clock input on the LCEVB

## 4.4. Debug Connector (P1)

The LCEVB has a single 14-pin keyed JTAG connector for connection to an external debugger.

Before attaching or removing the debug cable from the LCEVB remove power from the EVB to prevent damage to the LCEVB or debug hardware.

#### 4.4.1. Debug Connector Pinout

The following tables list the pinout for the JTAG connector used on the LCEVB

Pin No Pin No Connection **Function Function** Connection TDI PC0 **GND GND** 3 TDO PC1 4 **GND GND** 5 **TCLK** PH9 6 **GND GND** 7 **EVTI** PL8 N/C 8 9 JTAG-RSTx PH10 RESET 10 TMS 11 VREF PER HVA 12 **GND GND** RDY 13 **JCOMP** 10K Pulldown 14

Table 3. 14-Pin JTAG Debug Connector Pinout

TDI, TDO and TMS have 10K pullup resistors on the LCEVB. TCLK has a 10K pulldown (R147) to facilitate STANDBY exit without any additional code (at the sacrifice of slightly higher STANDBY current), however this can be changed to a pullup if required by removing R147 and fitting the resistor on R56.

| TERMINAL TYPE <sup>1</sup> | TERMINAL TYPE <sup>1</sup> POWERUP pad state <sup>2</sup> |                | DEFAULT pad state <sup>3</sup> |

|----------------------------|-----------------------------------------------------------|----------------|--------------------------------|

| RESET                      | RESET strong pull-down                                    |                | weak pull-up                   |

| PORST <sup>4</sup>         | Weak pull down                                            | Weak pull up   | weak pull-up                   |

| GPIO                       | high impedance                                            | high impedance | high impedance                 |

| ANALOG                     | ANALOG high impedance                                     |                | high impedance                 |

| EOUT0, EOUT1               | high impedance                                            | high impedance | high impedance                 |

| TCK                        | high impedance                                            | weak pull-up   | weak pull-up                   |

| TMS high impedance         |                                                           | weak pull-up   | weak pull-up                   |

| TDI high impedanc          |                                                           | weak pull-up   | weak pull-up                   |

| TDO                        | high impedance                                            | high impedance | high impedance                 |

Table 4. JTAG Pins Pull State (from MPC5748G Reference Manual)

## 5. Communications & Memory Interfaces:

This section details the communication interface and storage peripherals that are implemented on the LCEVB.

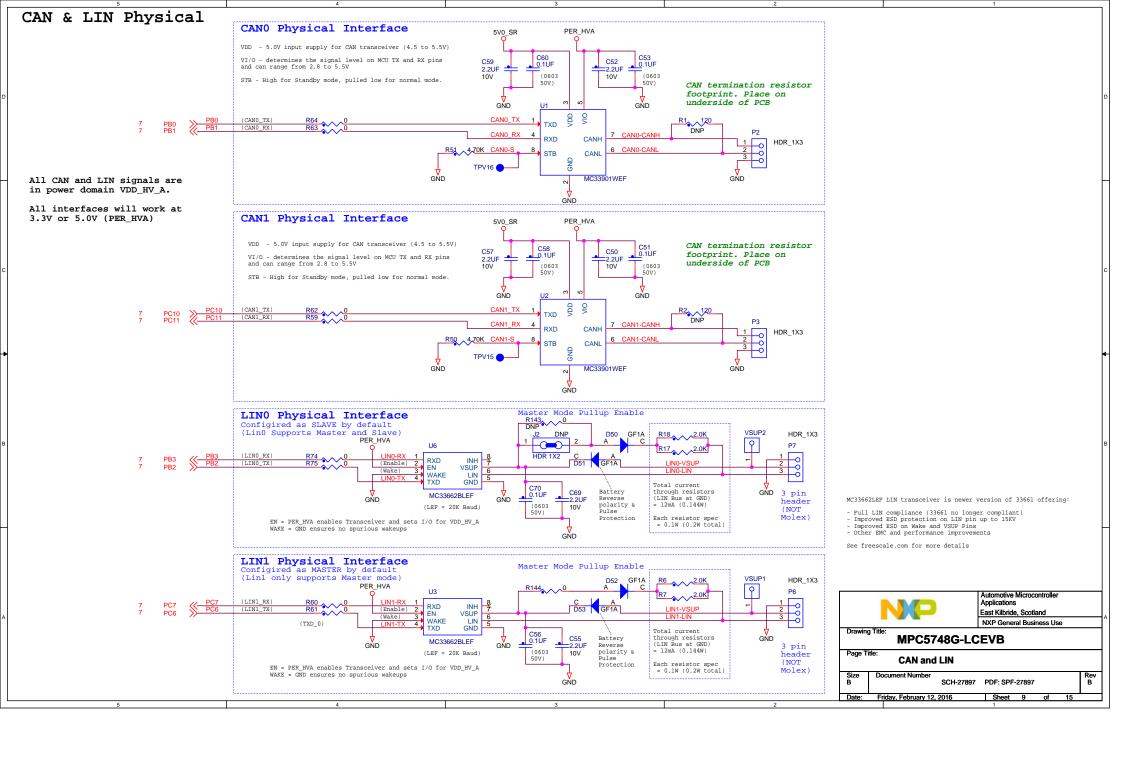

### 5.1. CAN Interfaces (P2, P3)

The LCEVB incorporates two identical CAN interface circuits connected to MCU CAN0 and CAN1 using MC33901 transceivers. Both transceivers are configured for high speed operation by pulling pin 8 to GND via a 4.7 KOhm resistor. There are test points to allow the Select pin to be driven high if desired. The MC33901 is pin compatible with other CAN transceivers supporting full CAN FD data rates.

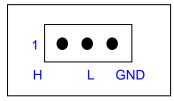

For flexibility, the CAN transceiver I/O is connected to a 0.1" header (P2 for CAN0 / P3 for CAN1) rather than using non-standard DB9 connectors. The pinout of these headers is shown below.

Figure 5. CAN Physical Interface Connectors

#### 5.2. LIN Interfaces (P6, P7)

The LCEVB incorporates two LIN transceiver circuits connected to MCU LIN0 and LIN1, using an NXP MC33662 transceiver. The MPC5748G LIN0 supports both master and slave modes whereas LIN1 only supports master mode.

On the LCEVB, the LIN0 transceiver is configured as slave mode by default. Master mode operation is possible by either populating a zero ohm resistor (R143) or buy fitting a jumper header (J2) – see the schematics for details. The LIN0 transceiver is hard wired for master mode.

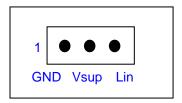

To save on board space and cost, both LIN transceivers are connected to 0.1" pitch 3x1 headers as shown below rather than the usual LIN Molex header.

Figure 6. LIN Physical Interface Connector

Note that in order for the LIN transceiver to function, external 12v must be supplied via pin 2 of the connector

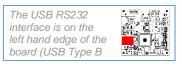

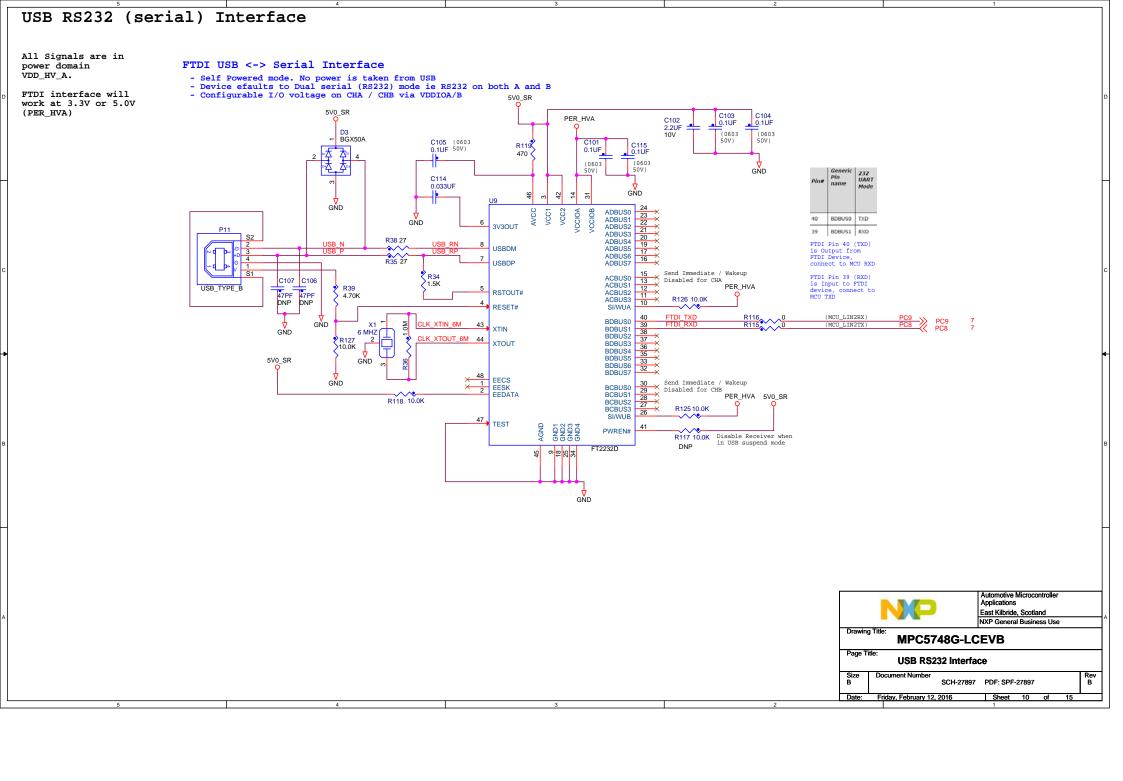

#### 5.3. USB RS232 Serial Interface (P11)

The LCEVB incorporates a USB RS232 serial interface providing RS232 connectivity via a direct USB connection between the PC and the EVB. The circuit contains an FTDI FT2232D USB to Serial interface which should automatically install the drivers for two additional COM ports on your PC. Note that only one of these ports is used so you will need to try both (usually the higher numbered COM port is the active one). For more information on the USB drivers and general fault finding, consult the FTDI website at <a href="http://www.ftdichip.com/">http://www.ftdichip.com/</a>

The MCU LIN2 signals are routed to the FTDI transceiver (UART TX and RX). No handshaking signals are implemented and no board configuration is required.

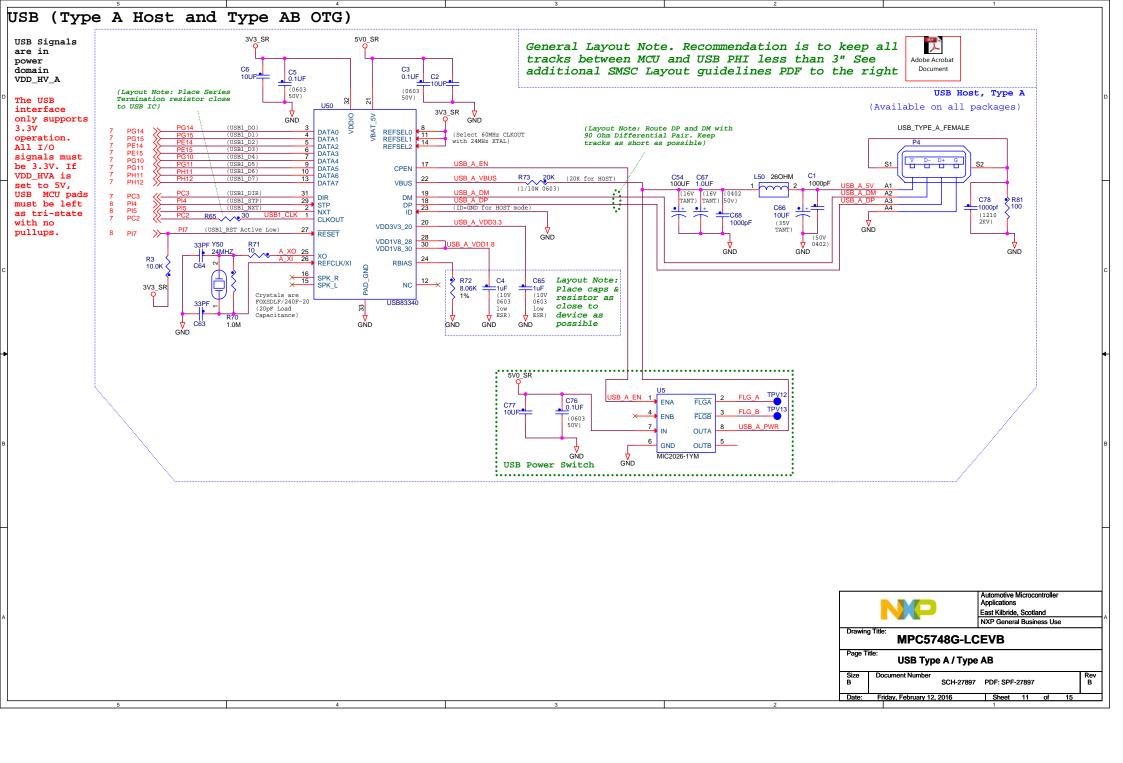

## 5.4. USB HOST Interface (P4)

The LCEVB includes a Type A (Host) USB interface, routed to a USB type A female connector. The USB circuit contains a USB83340 transceiver with a MIC2026-1YM USB power switch. There is no hardware user configuration required to use the USB circuit.

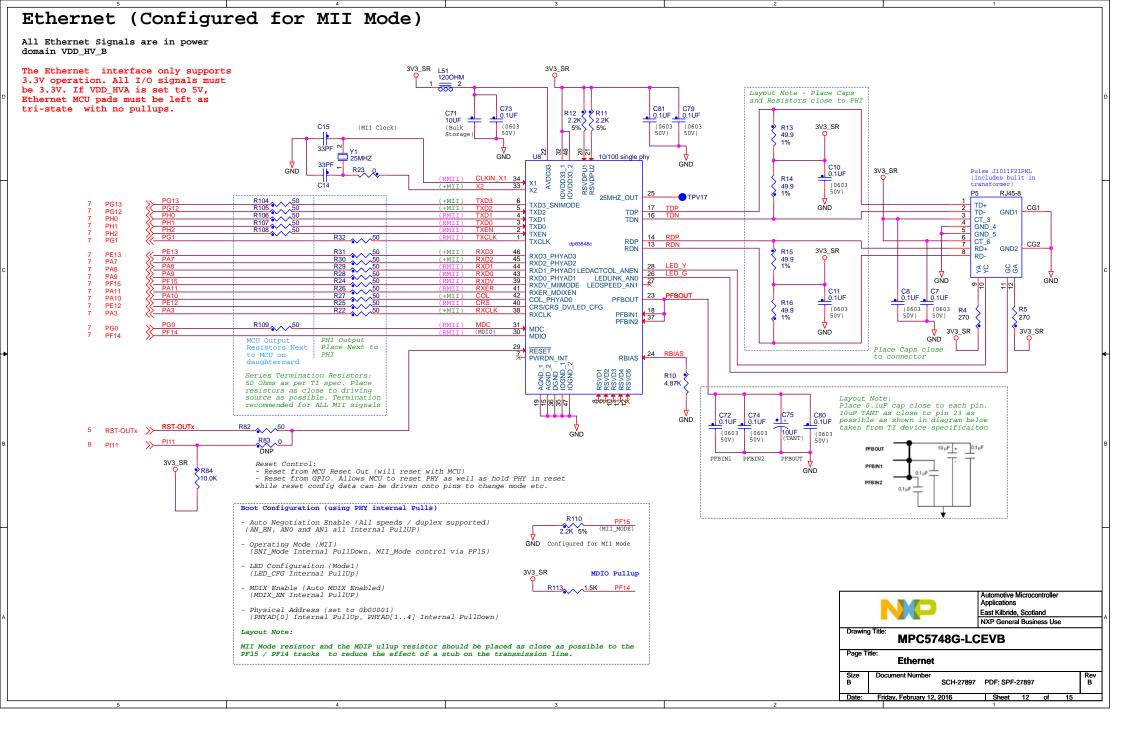

#### 5.5. Ethernet Interface (P5)

The Ethernet interface is mid-way along the top edge of the LCEVB

The EVB incorporates a single DP83848c Ethernet transceiver with the circuitry configured for MII mode. The transceiver is connected to a pulse J1011F21PNL RJ45 connector which includes a built-in isolation transformer. There is no hardware configuration needed.

If you require RMII mode or access to both Ethernet ports on the MPC5748G, please purchase the MPC5748G customer EVB and appropriate daughter cards.

Note that the MCU Ethernet signals are all in the VDD\_HV\_B domain. The Ethernet PHY will only function with 3.3 V I/O so if you have made any modifications to the EVB power domain configuration (via the zero ohm resistors), you need to ensure the VDD\_HV\_B domain is at 3.3 V before attempting to use the Ethernet module. If VDD\_HV\_B is set to 5 V, the signals routed to the Ethernet PHY (see the EVB schematics) must be left as tristate to prevent damage to the transceiver.

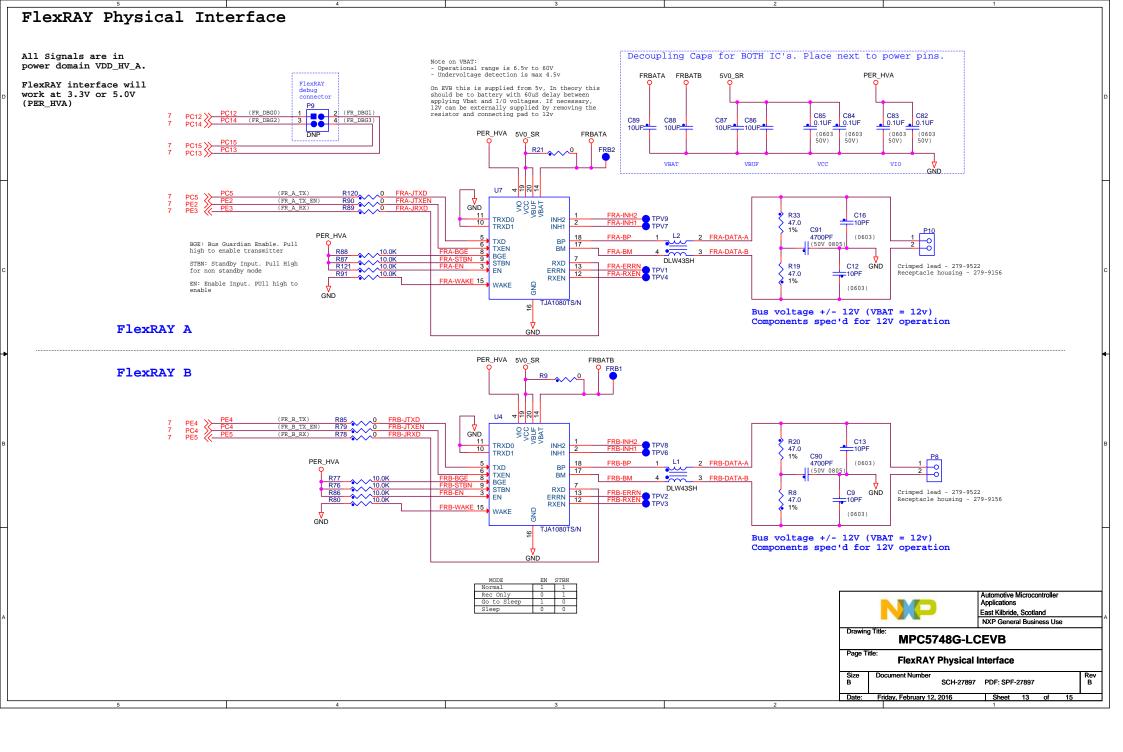

## 5.6. FlexRay (P8, P9, P10)

The FlexRay interfaces are midway down the left hand edge of the LCEVB

The LCEVB incorporates two FlexRay TJA1080TS/N interfaces connected to MCU FlexRay channels A and B and routed to two Molex 1.25 mm pitch PicoBlade shrouded headers (standard on many NXP EVB's). There is no hardware configuration required to use FlexRay.

Note that the LCEVB is supplied with a 40 MHz crystal by default. If FlexRay is configured to use the external clock source, then the crystal should be left at 40 MHz.

## 6. User Interface (I/O)

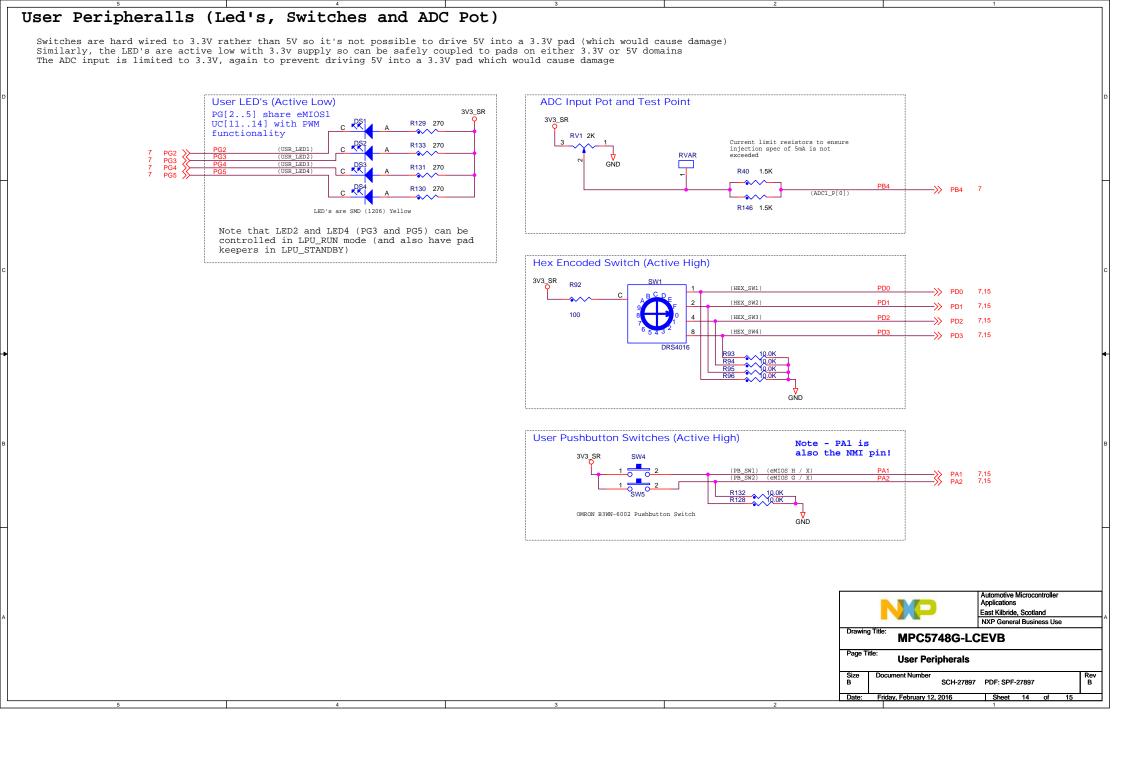

This section details the user I/O available on the LCEVB and includes the GPIO matrix, switches, LED's and the ADC variable resistor.

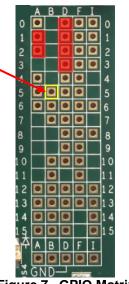

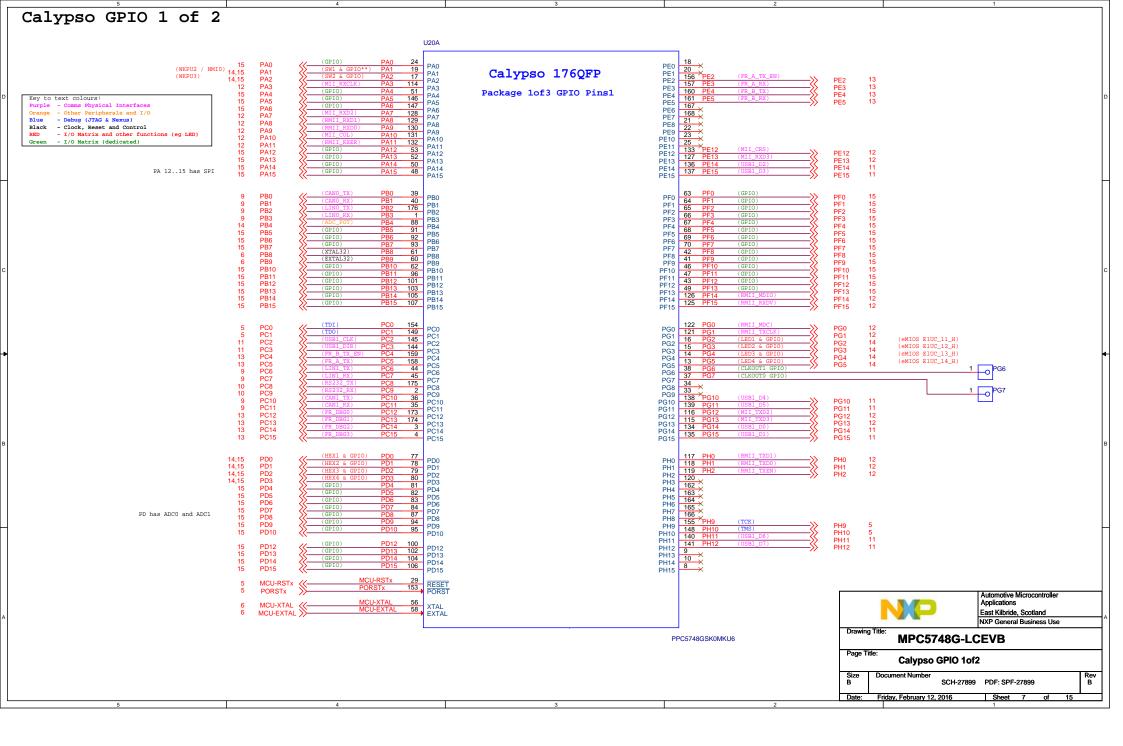

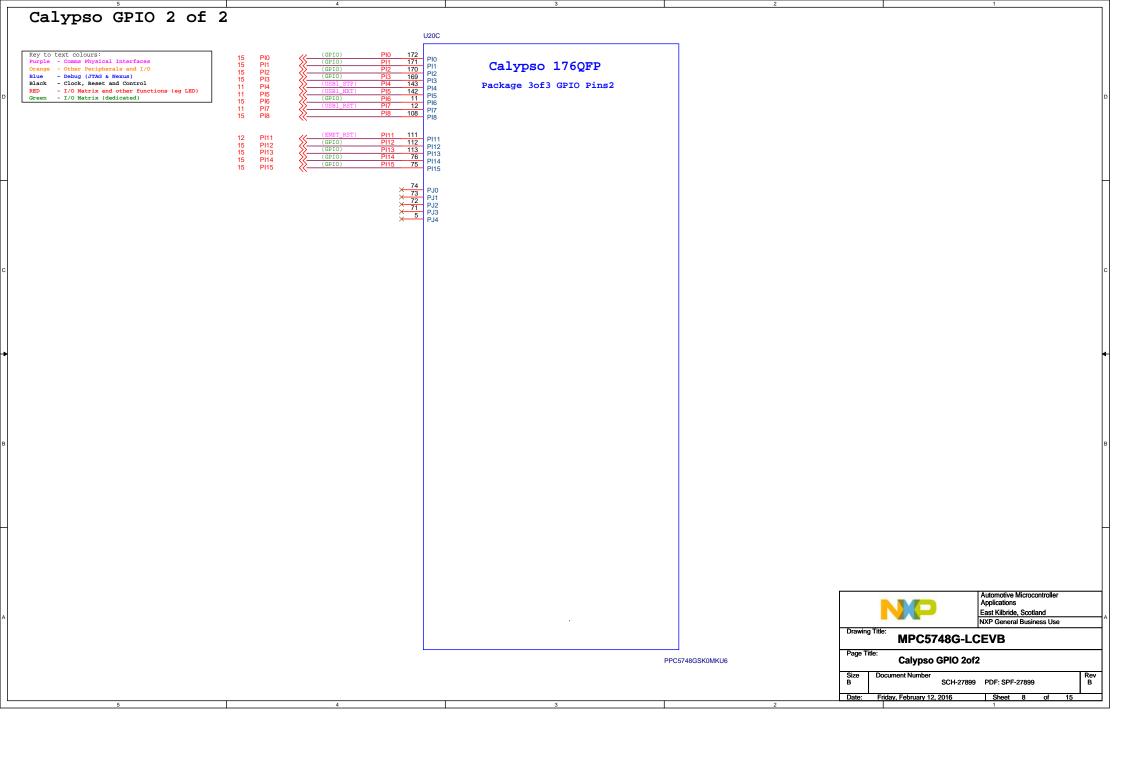

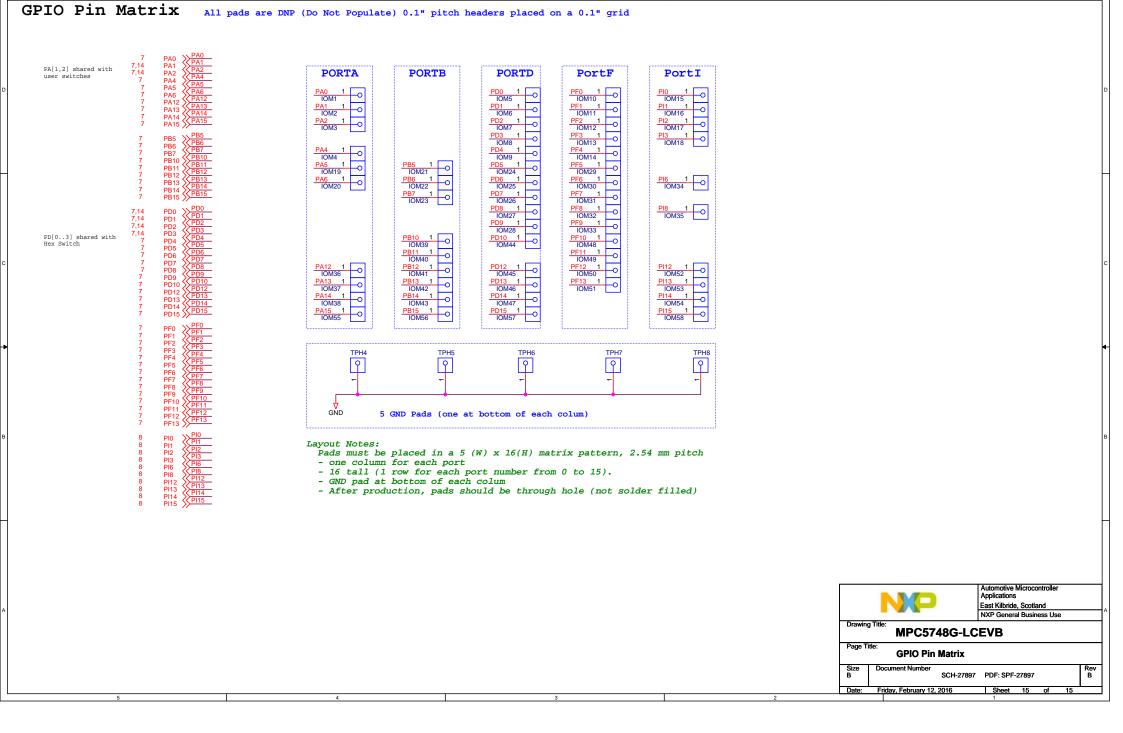

#### 6.1. GPIO Matrix

The GPIO matrix is on the right hand edge of the LCEVB

A sub-set of available GPIO pins (available pins being those not already routed to LCEVB peripherals) are available at the GPIO matrix as detailed below. The matrix provides an easy to follow, intuitive, space saving grid of 0.1" header through-hole pads. Users can solder wires, fit headers or simply insert a scope probe into the respective pad.

To use the matrix, simply read the port letter from the top or bottom row of text then the pad number from the columns on the left or right of the matrix. For example, the 1<sup>st</sup> pad available on Port B is PB5 as outlined below.

Figure 7. GPIO Matrix

If a pad is populated in the matrix, it means this is available for exclusive use as GPIO. The exception to this are the port pins detailed below which are also shared with switches or user LED's (shaded red in the matrix diagram above).

PD0, PD1, PD2, PD3 – HEX Encoder Switch PA1, PA2 – User pushbutton Switches

If you require access to all of the available GPIO pads, the customer EVB and daughtercard provides this additional functionality.

## 6.2. User Switches (SW4, SW5)

The user pushbutton switches are in the bottom right corner of the LCEVB

There are two active high (pulled low, driven to 3.3 V) pushbutton switches on the LCEVB connected directly to MCU GPIO ports. No configuration is required to use the switches.

SW4 is connected to port PA1 (which is also the NMI pin) and SW5 is connected to port PA2

#### **NOTE**

The MCU ports used on the user pushbutton switches are also routed to the GPIO matrix.

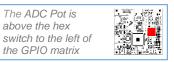

## 6.3. Hex Encoded Switch (SW1)

The hex encoder switch is located to the left of the GPIO Matrix

There is a single hex encoded 16 position rotary switch on the LCEVB. This outputs a binary encoded hex value (active high) on four MCU ports (Port D[0..3]).

HEX SW4 HEX SW3 HEX SW2 HEX SW1 **Position** (PD3) (PD2) (PD1) (PD0) A В  $\mathbf{C}$ D Ε F

Table 5. Hex Encoder Switch (SW2)

Note that POSN 0 will ensure that no voltage is applied to the pads. This allows the pads to be used as normal GPIO (with 10K pulldown) and accessed at the respective pads on the GPIO matrix area.

### 6.4. User LED's (DS1, DS2, DS3, DS4)

The user LED's are above the user switches in the lower right corner

There are four **active low** user LED's, DS1 to DS4, connected directly to 4 MCU ports (PG[2..5]) as shown below. No configuration is required to use the LED's.

Table 6. Use LED's (DS1, DS2, DS3 and DS4)

| User LED | MCU Pin |

|----------|---------|

| DS1      | PG2     |

| DS2      | PG3     |

| DS3      | PG4     |

| DS4      | PG5     |

#### 6.5. ADC Input Potentiometer (RVAR, RV1)

There is a small variable resistor RV1 on the LCEVB which routes a voltage between 0v and 3.3 V to MCU pin PB4. This is useful for quick ADC testing. Test point RVAR can be used to probe the voltage with a voltmeter.

Note that this circuit provides a very rough way to evaluate the ADC. There is a small current limiting series resistor network to limit the injection current to around 4.4 mA.

## 7. MCU Port Pin LCEVB Functions

The table below shows what each MCU pin is used for on the LCEVB.

Table 7. LCEVB 176QFP Port Pin Functions

| No | Port A            | Port B    | Port C    | Port D            | Port E    | Port F   | Port G   | Port H   |  |

|----|-------------------|-----------|-----------|-------------------|-----------|----------|----------|----------|--|

| 0  | GPIO              | CAN0      | JTAG      | GPIO <sup>3</sup> |           | GPIO     | Ethernet | Ethernet |  |

| 1  | GPIO <sup>2</sup> | CAN0      | JTAG      | GPIO <sup>3</sup> |           | GPIO     | Ethernet | Ethernet |  |

| 2  | GPIO <sup>2</sup> | LIN0      | USB1      | GPIO <sup>3</sup> | FlexRay A | GPIO     | GPIO 4,  | Ethernet |  |

| 3  | Ethernet          | LIN0      | USB1      | GPIO <sup>3</sup> | FlexRay A | GPIO     | GPIO 4   |          |  |

| 4  | GPIO              | ADC Pot   | FlexRay B | GPIO              | FlexRay B | GPIO     | GPIO 4   |          |  |

| 5  | GPIO              | GPIO      | FlexRay A | GPIO              | FlexRay B | GPIO     | GPIO 4   |          |  |

| 6  | GPIO              | GPIO      | LIN1      | GPIO              |           | GPIO     | GPIO     |          |  |

| 7  | Ethernet          | GPIO      | LIN1      | GPIO              |           | GPIO     | GPIO     |          |  |

| 8  | Ethernet          | EXTAL32   | RS232     | GPIO              |           | GPIO     |          |          |  |

| 9  | Ethernet          | XTAL32    | RS232     | GPIO              |           | GPIO     |          | JTAG     |  |

| 10 | Ethernet          | SAI Audio | CAN1      | GPIO              |           | GPIO     | USB1     | JTAG     |  |

| 11 | Ethernet          | GPIO      | CAN1      |                   |           | GPIO     | USB1     | USB1     |  |

| 12 | GPIO              | GPIO      | FlexRay   | GPIO              | Ethernet  | GPIO     | Ethernet | USB1     |  |

| 13 | GPIO              | GPIO      | FlexRay   | GPIO              | Ethernet  | GPIO     | Ethernet |          |  |

| 14 | GPIO              | GPIO      | FlexRay   | GPIO              | USB1      | Ethernet | USB1     |          |  |

| 15 | GPIO              | GPIO      | FlexRay   | GPIO              | USB1      | Ethernet | USB1     |          |  |

| No | Port I   | Port J |

|----|----------|--------|

| 0  | GPIO     |        |

| 1  | GPIO     |        |

| 2  | GPIO     |        |

| 3  | GPIO     |        |

| 4  | USB1     |        |

| 5  | USB1     |        |

| 6  | GPIO     |        |

| 7  | USB1     |        |

| 8  | GPIO     |        |

| 9  |          |        |

| 10 |          |        |

| 11 | Ethernet |        |

| 12 | GPIO     |        |

| 13 | GPIO     |        |

| Key: |                                      |

|------|--------------------------------------|

|      | Pin not bonded out on 176QFP package |

|      | Pin not accessible on LCEVB          |

GPIO GPIO

14

15

<sup>&</sup>lt;sup>2</sup> Shared with user switches

<sup>&</sup>lt;sup>3</sup> Shared with Hex Encoder Switch

<sup>&</sup>lt;sup>4</sup> Shared with user LED's

## 8. Appendix

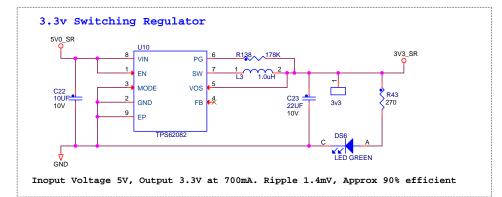

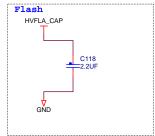

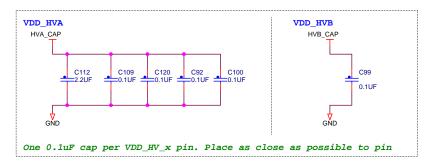

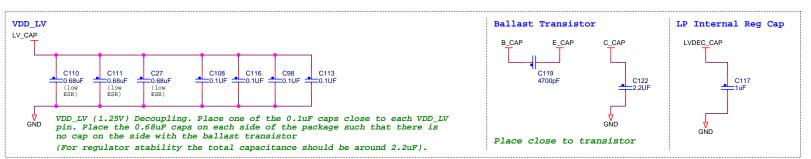

The MPC5748G LCEVB schematics, Rev B are shown below.

## MPC5748G Low Cost Evaluation Board (MPC5748G-LCEVB)

| Table Of Contents:                                    |          |  |  |  |  |  |

|-------------------------------------------------------|----------|--|--|--|--|--|

| Power - Main input and 3.3V regulator                 | Sheet 2  |  |  |  |  |  |

| Power - MCU Power                                     | Sheet 3  |  |  |  |  |  |

| Power - MCU Decoupling                                | Sheet 4  |  |  |  |  |  |

| Reset and JTAG                                        | Sheet 5  |  |  |  |  |  |

| Clocks                                                | Sheet 6  |  |  |  |  |  |

| MCU GPIO 1                                            | Sheet 7  |  |  |  |  |  |

| MCU GPIO 2                                            | Sheet 8  |  |  |  |  |  |

| Comms1 - CAN and LIN                                  | Sheet 9  |  |  |  |  |  |

| Comms 2 - FTDI RS232 Interface                        | Sheet 10 |  |  |  |  |  |

| Comms 3 - USB Host Interface (device footprints only) | Sheet 11 |  |  |  |  |  |

| Comms 4 - Ethernet (MII Mode)                         | Sheet 12 |  |  |  |  |  |

| Comms 5 - FlexRay                                     | Sheet 13 |  |  |  |  |  |

| User - Switches, LED's and Potentiometer              | Sheet 14 |  |  |  |  |  |

| User - GPIO Pin Matrix                                | Sheet 15 |  |  |  |  |  |

#### Caution:

These schematics are provided for reference purposes only. As such, NXP does not make any warranty, implied or otherwise, as to the suitability of circuit design or component selection (type or value) used in these schematics for hardware design using the NXP Calypso family of Microprocessors. Customers using any part of these schematics as a basis for hardware design, do so at their own risk and NXP does not assume any liability for such a hardware design.

#### Notes:

- All components and board processes are to be ROHS compliant

- All small capacitors are 0402 unless otherwise stated

- All resistors are 0603 5% 0.1w unless otherwise stated. All zero ohm links are 0603

- All connectors and headers are denoted Px and are 2.54mm pitch unless otherwise stated

- All jumpers are denoted Jx. Jumpers are 2mm pitch

- Jumper default positions are shown in the schematics. For 3 way jumpers, default is always posn 1-2. 2 Pin jumpers generally have the "source" on pin 1.

- All switches are denoted SWx

- All test points (SMT wire loop style) are denoted TPx

- Test point Vias (just through hole pads) are denoted TPVx

Signals (ports) have not been routed via busses as this makes it harder to determine where each signal goes.

User notes are given throughtout the schematics.

Specific PCB LAYOUT notes are detailed in ITALICS

#### Revision Information

| Rev | Date        | Designer           | Comments                                                      |

|-----|-------------|--------------------|---------------------------------------------------------------|

| x1  | 14 Apr 2015 | Alasdair Robertson | Start of capture, Working version (256BGA)                    |

| x2  | 08 May 2015 | Alasdair Robertson | Changed to 176 QFP Package and changed periperhal Matrix      |

| х3  | 18 May 2015 | Alasdair Robertson | Changes required for initial placement                        |

| x4  | 19 May 2015 | Alasdair Robertson | Tidy Up, Replaced some "hard to source" components            |

| x5  | 26 May 2015 | Alasdair Robertson | Renumber and Back Annoted from Layout                         |

| х6  | 27 May 2015 | Alasdair Robertson | Correction to GND on 3v3 Regulator circuit                    |

| x7  | 29 May 2015 | Alasdair Robertson | Correction to CAN Test points                                 |

| x8  | 31 May 2015 | Alasdair Robertson | Few refdes changes after layout tweaks                        |

| x9  | 01 Jun 2015 | Alasdair Robertson | Correction to user LED Refdes after re-number                 |

| x10 | 01 Jun 2015 | Alasdair Robertson | DNP Jumpers. 0 Ohm resistors added accross LIN jumpers        |

| A   | 11 Jun 2015 | Andrew MacDonald   | Prototype Manufacture Release                                 |

| AX1 | 29 Sep 2015 | Alasdair Robertson | Prodn Build changes (LIN0 default to Slave, LIN1 Master only) |

|     |             |                    | PN Changed to MPC5748G-LCEVB                                  |

| AX2 | 26 Oct 2015 | Alasdair Robertson | Change to JTAG Pulls to meet latest RM Spec                   |

| AX3 | 29 Oct 2015 | Alasdair Robertson | Changed RV1 current limit resistor. SW4 / SW5 refdes swap     |

| AX4 | 09 Dec 2015 | Alasdair Robertson | Pull DOWN on TCLK to mitigate against STANDBY exit issue.     |

| AX5 | 20 Jan 2016 | Alasdair Robertson | Updated NXP Logos                                             |

| В   | 12 Feb 2016 | Alasdair Robertson | Updated NXP Logos                                             |

3 Different test points used in design:

TPVx - Through Hole Pad small

TPHx - Through Hile Pad Large (for standard 0.1" header). Also used on IO Matrix (IOMx)

TPX - Surface Mount Wire Loop

|                   | 25     | Last Kilbride, Ocolland                                                                                              |     |

|-------------------|--------|----------------------------------------------------------------------------------------------------------------------|-----|

| - 4               |        | NXP General Business Use                                                                                             |     |

|                   |        | ation proprietary to NXP and shall not be used for engin-<br>whole or in part without the express written permission | • • |

| igner:<br>bertson | Drawin | MPC5748G-LCEVB                                                                                                       |     |

| wn by:<br>bertson | Page T | itle:<br>Index and Title Page                                                                                        |     |

| roved:            | Size   | Document Number                                                                                                      | Rev |

| _          | NO. |   | - | - |

|------------|-----|---|---|---|

|            | N   | M | 7 |   |

| <b>1</b> 7 | - 1 | м | K |   |

| -          | 43  | ٥ |   |   |

**Automotive Microcontroller Applications** East Kilbride, Scotland

| Designer:<br>A. Robertson |           | MPC5748G-LCEVB                   |           |       |      |    |          |  |  |

|---------------------------|-----------|----------------------------------|-----------|-------|------|----|----------|--|--|

| Drawn by:<br>A. Robertson | Page Ti   | Page Title: Index and Title Page |           |       |      |    |          |  |  |

| Approved:<br>A. Robertson | Size<br>B | Document Number<br>SCH-27897     | PDF: SPF- | 27897 |      |    | Rev<br>B |  |  |

|                           | Date:     | Friday, February 12, 2016        | Sheet     | 1     | of 1 | 15 |          |  |  |

| 2                         |           |                                  | 1         |       |      |    |          |  |  |

Automotive Microcontroller

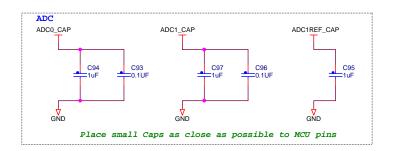

#### Calypso MCU Decoupling and bulk storage

# Capacitor Types: 4700pF - Ceramic X7R, 50V 10% 0402 0.1uF - Ceramic X7R, 16V 10% 0402 (Kemet C0402C104K4RAC) 0.68uF - Ceramic X7R, 16V 10% 0805 (Murata GCM219R71C684KA37) 1uF - Ceramic X7R, 10V 10% 0603 Low ESR (Taiyo Yuden LMK107B7105KA-T) 2.2uF - Ceramic X7R, 10V 10% 0603 Low ESR (Taiyo Yuden LMK107B7225KA-TR)

5

How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE, MIFARE CLASSIC, MIFARE DESFIRE, MIFARE HUS, MIFARE, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big,LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2016 NXP B.V.

Document Number: MPC5748GLCEVBUG Rev. 0 05/2016